### Vivid: An Operating System Kernel for Radiation-Tolerant Flight Control Software

by

Cel Andromeda Skeggs

Bachelor of Science in Computer Science and Engineering Massachusetts Institute of Technology, 2020

Submitted to the Department of Electrical Engineering and Computer Science in partial fulfillment of the requirements for the degree of

Master of Engineering in Electrical Engineering and Computer Science at the Massachusetts Institute of Technology

May 2022

© 2022 Massachusetts Institute of Technology. All Rights Reserved.

Signature of Author:

Department of Electrical Engineering and Computer Science May 15, 2022

Certified by:

M. Frans Kaashoek Charles Piper Professor Thesis Supervisor

Accepted by:

Katrina LaCurts Chair, Master of Engineering Thesis Committee

### Vivid: An Operating System Kernel for Radiation-Tolerant Flight Control Software

by

Cel Andromeda Skeggs

Submitted to the Department of Electrical Engineering and Computer Science on May 15, 2022 in Partial Fulfillment of the Requirements for the Degree of Master of Engineering in Electrical Engineering and Computer Science

#### ABSTRACT

This thesis considers the challenge of defending flight software from radiation errors without a radiation-hardened processor. A new real-time operating system, *Vivid*, explores the use of redundant multithreading to protect critical software components from radiation errors, and offers new abstractions to reduce the number of single points of vulnerability in the system. It introduces a static component initialization system for C, which eliminates most runtime initialization steps from the operating system and flight software. It introduces a partition scheduler based on *execution clips*, which ensures that software components always start from a safe state, and it protects the system's safe state using a pair of memory scrubbers. Vivid introduces *voting ducts*, an inter-process communication primitive for redundant multithreading that eliminates single points of vulnerability from the voting process. Finally, it defines a *sequence of repair* that ultimately grounds the correct operation of all components in the system's software in a hardware watchdog.

To demonstrate the applicability and effectiveness of Vivid, this thesis introduces *Swivel*, a testbench spacecraft, and describes *SwivelFSW*, which is the implementation of flight software that meets Swivel's behavioral requirements, and *SwivelSim*, which is the simulation of Swivel's avionics. Next, this thesis introduces *Hailburst*, a system for efficient processor emulation and radiation fault injection, and uses it to evaluate Vivid's radiation tolerance through a series of accelerated radiation injection trials. In the tested configuration, Vivid tolerates approximately 149 out of every 150 injected radiation faults without any observed requirement failures, and recovers from the remaining 1 out of 150 radiation faults within at most 2.05 seconds of recovery time in the worst observed case. Because some of Vivid's defenses appear to be more effective than others, and some may be counterproductive, this thesis discusses future work that would be required before Vivid's abstractions could be applied to real-world flight software.

Thesis Supervisor: M. Frans Kaashoek Title: Charles Piper Professor

# Acknowledgements

The past sixteen months have been challenging, even beyond the regular difficulty of a Master's program. The COVID-19 pandemic, already ongoing, continues to stretch interminably into the future, and affects every decision I make. Geopolitical tensions have risen, both here and around the world: Russia is invading Ukraine, unchecked industrial pollution continues to upset our world's climate and plunge us towards a dangerous future, and lawmakers and public figures across the United States continue to threaten the legal and physical safety of people like me.

Because of these challenges, I have a great deal of gratitude to share for too many people to list here for helping me survive and sometimes even thrive in this difficult period of history. I am extremely thankful for the endless support I have received from Frans, my advisor, whose active mentorship made this thesis possible. I also owe a great deal to Beth, my mother; when I needed to go into major surgery on short notice midway through this semester, she set aside her obligations to fly across the country and help me stumble through the hospital and the first weeks of my recovery; I also owe much gratitude to the rest of my friends that assisted with my recovery even when it was inconvenient to them.

I very much appreciate the support I have received throughout the whole of my degree program from the rest of my immediate and extended family, and I value greatly the companionship, advice, and common sense that my dear network of friends, near and far, have provided through this whole period of my life. I also harbor a great deal of appreciation for everyone else in my lab, PDOS, whose camaraderie, ideas, and knowledge helped me grow more confident in and cognizant of myself and my research over the course of the past year and a half, and I am very thankful to all of the mentors and coworkers at JPL that I worked with before entering this program, who made my interest in this area of research possible.

# Table of Contents

| 1. Introduction                                   | 7  |

|---------------------------------------------------|----|

| 1.1. Motivation                                   | 7  |

| 1.2. State of the Art                             | 8  |

| 1.3. New Approach                                 | 10 |

| 1.4. Contributions and Results                    | 11 |

| 1.5. Source Code Overview                         | 15 |

| 1.6. Outline                                      | 15 |

| 2. Related Work                                   | 17 |

| 2.1. Radiation Defense                            | 17 |

| 2.2. Fault Injection                              | 20 |

| 3. Design of the Vivid Kernel                     | 24 |

| 3.1. Redundant Applications on Vivid              | 25 |

| 3.2. Structure of Vivid's Kernel                  | 27 |

| 3.3. Vivid API Overview                           | 29 |

| 3.4. Output and State Voting                      | 31 |

| 3.4.1. Lockstep Scheduling                        | 34 |

| 3.4.2. State Resynchronization                    | 35 |

| 3.4.3. Voting Duct Structure                      | 37 |

| 3.4.4. Replicated Components                      | 39 |

| 3.4.5. Prepare/Commit Drivers                     | 40 |

| 3.5. Static Component System                      | 42 |

| 3.5.1. Static Memory Management                   | 44 |

| 3.5.2. Execution Clips                            | 45 |

| 3.5.3. Code Replication Linker                    | 47 |

| 3.6. Safety Properties                            | 48 |

| 3.6.1. Transparent Recovery                       | 49 |

| 3.6.2. Fallback Recovery                          | 50 |

| 3.6.3. Missing Safety Features                    | 52 |

| 4. Implementation of the Vivid Kernel             | 53 |

| 4.1. Debug Log System                             | 53 |

| 4.2. Watchdog Device                              | 58 |

| 4.3. Replication Linker                           | 61 |

| 4.4. Initialization Hooks and Type Erasure        | 64 |

| 4.5. Context Switching in the Partition Scheduler | 65 |

| 4.6. Clip Duration Calibration                    | 66  |

|---------------------------------------------------|-----|

| 4.7. Kernel Loading and Scrubbing                 | 67  |

| 4.8. Build System                                 | 68  |

| 4.9. Reliability Configuration                    | 68  |

| 5. The Swivel Spacecraft                          | 70  |

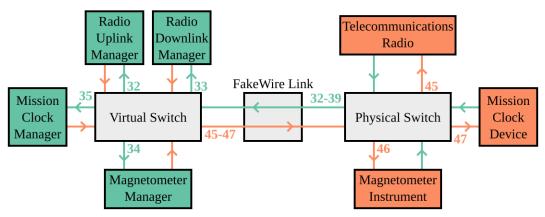

| 5.1. Spacecraft Avionics                          | 70  |

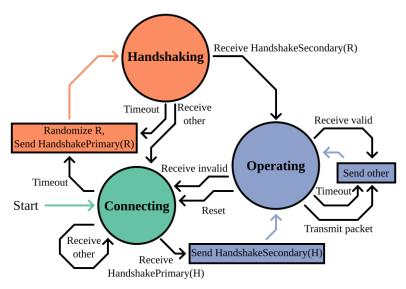

| 5.1.1. FakeWire Protocol                          | 72  |

| 5.1.2. SpaceWire Network Switch                   | 75  |

| 5.1.3. Mission Clock                              | 76  |

| 5.1.4. Radio                                      | 77  |

| 5.1.5. Magnetometer                               | 78  |

| 5.1.6. Commands and Telemetry                     | 79  |

| 5.2. Flight Software Requirements                 | 82  |

| 5.2.1. Command Handling Requirements              | 83  |

| 5.2.2. Telemetry Handling Requirements            | 84  |

| 5.2.3. Housekeeping Requirements                  | 85  |

| 5.2.4. Magnetometer Power Management Requirements | 85  |

| 5.2.5. Magnetometer Data Collection Requirements  | 86  |

| 6. The SwivelFSW Flight Software                  | 87  |

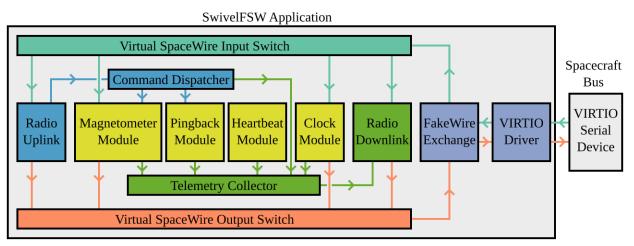

| 6.1. Flight Software Overview                     | 87  |

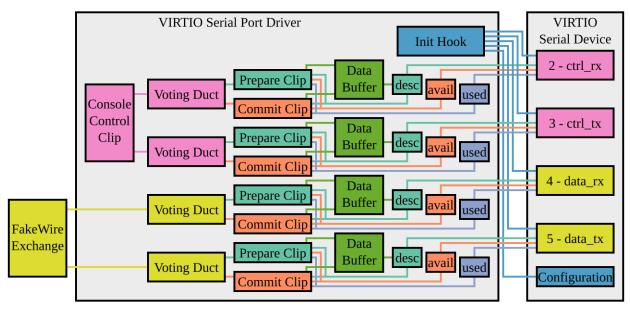

| 6.2. VIRTIO Driver                                | 89  |

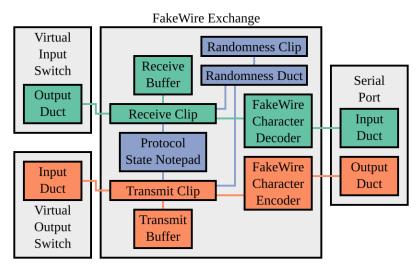

| 6.3. FakeWire Exchange                            | 91  |

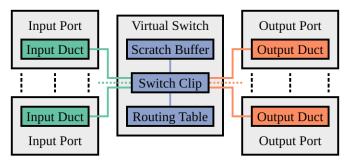

| 6.4. SpaceWire Virtual Switches                   | 92  |

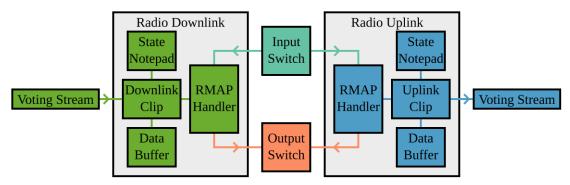

| 6.5. Radio Uplink and Downlink                    | 94  |

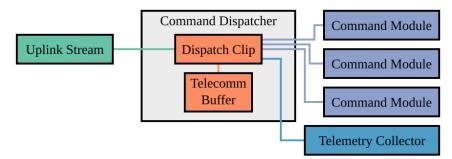

| 6.6. Command Dispatcher                           | 97  |

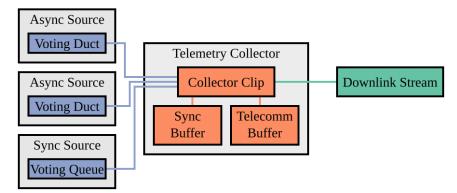

| 6.7. Telemetry Collector                          | 98  |

| 6.8. Magnetometer Module                          | 99  |

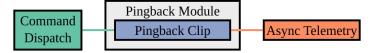

| 6.9. Pingback Module                              | 100 |

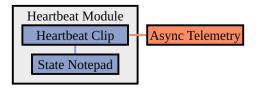

| 6.10. Heartbeat Module                            | 101 |

| 6.11. Mission Clock Module                        | 101 |

| 6.12. Schedule Order                              | 103 |

| 7. The SwivelSim Avionics Simulation              | 105 |

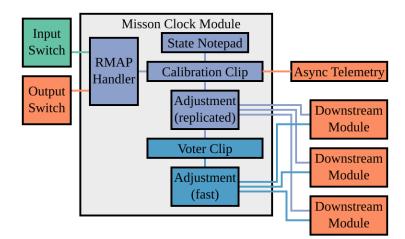

| 7.1. Simulation Overview                          | 106 |

| 7.2. QEMU Machine Configuration                   | 107 |

| 7.3. Timesync Protocol                            | 108 |

| 7.4. Watchdog Device                              | 109 |

| 7.5. Spacecraft Bus Simulation                    | 110 |

| 7.6. Analysis Tools                     | 111 |

|-----------------------------------------|-----|

| 7.6.1. Viterbi Analyzer                 | 111 |

| 7.6.2. Debug Log Extractor              | 117 |

| 7.6.3. Chart Renderer                   | 117 |

| 8. The Hailburst Fault Injection System | 118 |

| 8.1. Fault Model                        | 118 |

| 8.2. Precise Fault Injection            | 119 |

| 9. Evaluation                           | 122 |

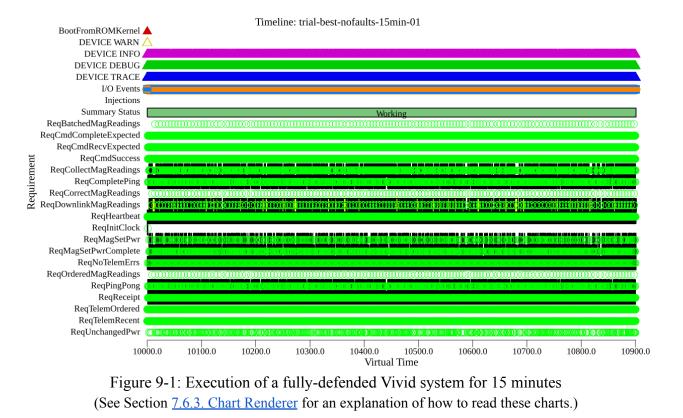

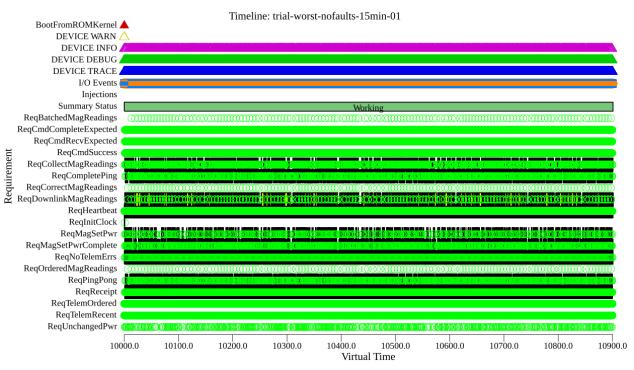

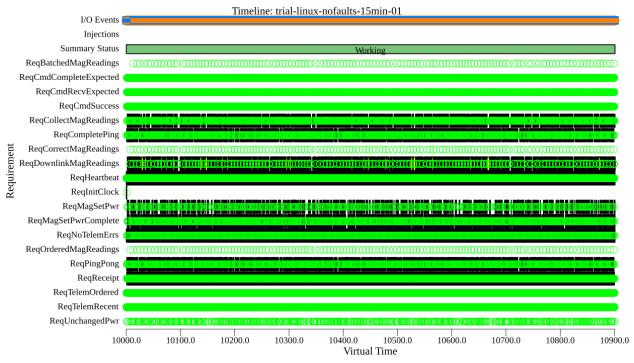

| 9.1. Application Correctness            | 122 |

| 9.2. Fault Injection Rates              | 125 |

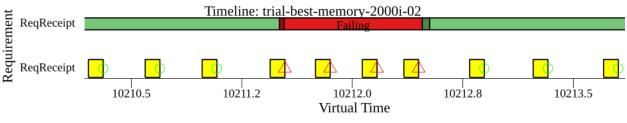

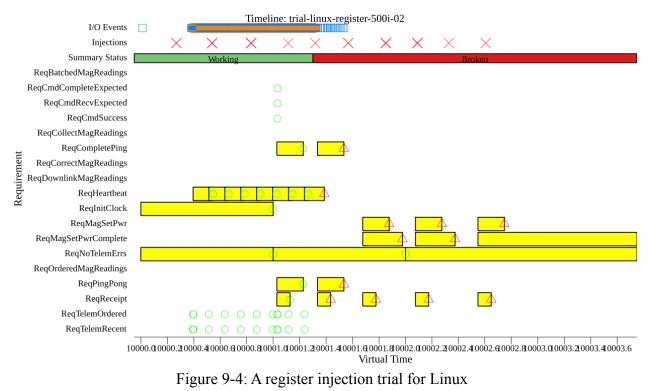

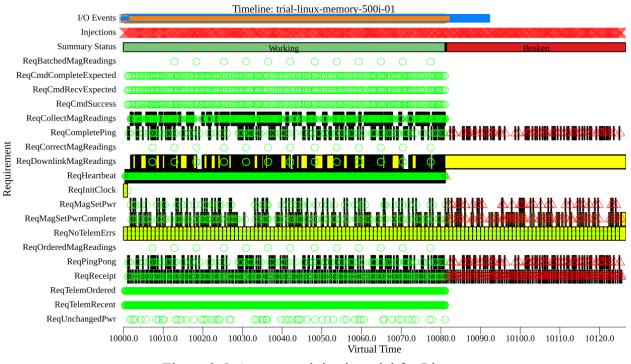

| 9.3. Fault Injection Demonstration      | 126 |

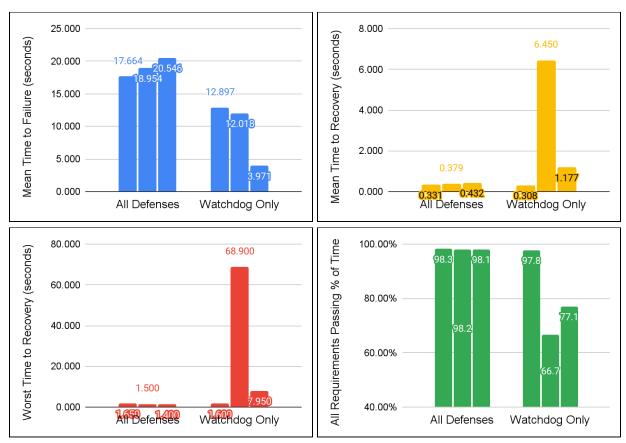

| 9.4. Reliability of Vivid               | 129 |

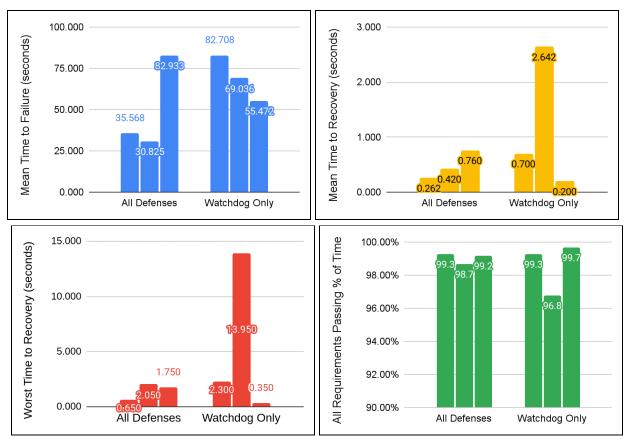

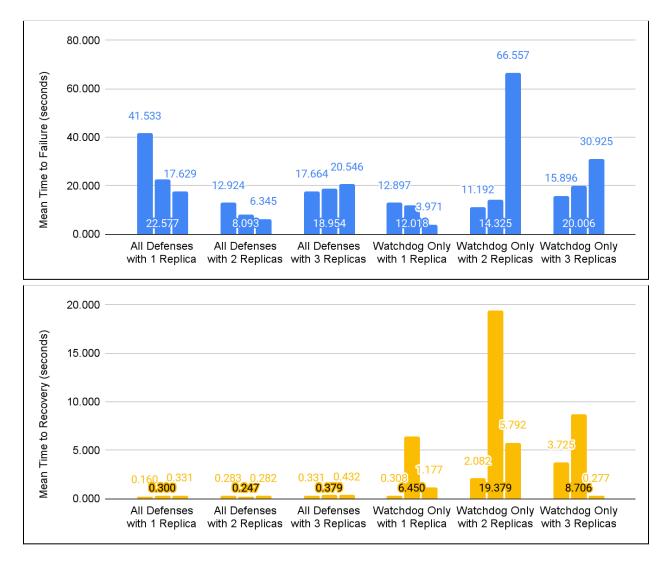

| 9.5. Triple Modular Replication         | 133 |

| 10. Future Work and Summary             | 139 |

| 10.1. Limitations                       | 139 |

| 10.2. Extensions                        | 141 |

| 10.3. Summary                           | 143 |

| Bibliography                            | 144 |

## 1. Introduction

This Master of Engineering thesis seeks to help flight computers on robotic spacecraft better tolerate the intense levels of radiation that they experience in space without requiring that they employ specialized radiation-hardened processors and memory. This thesis introduces five new systems: *Vivid*, a hard-real-time operating system designed for building radiation tolerant applications on unsafe hardware; *Hailburst*, a fault injection and processor emulation framework for measuring the effects of injecting accelerated radiation faults into spacecraft software; *Swivel*, a testbench spacecraft with requirements representative of realistic requirements for flight systems; *SwivelFSW*, an implementation of flight software for Swivel that demonstrates the usability and effectiveness of Vivid; and *SwivelSim*, an avionics simulation for Swivel that continuously tests the spacecraft against its requirements.

### 1.1. Motivation

Earth's magnetosphere protects terrestrial electronic systems from the high levels of radiation that are present in space, which can temporarily or permanently damage electronic systems. Robotic spacecraft, including satellites and deep-space probes, are especially vulnerable to radiation damage, as they rely on onboard computers for their basic ability to function. If a spacecraft's flight computer malfunctions, the spacecraft may be lost forever: it is generally impossible (or at least infeasible) to send anyone to repair it, and if the spacecraft cannot communicate with mission control, engineers on Earth will not have the data to diagnose the problem, nor the ability to conduct any repairs (such as resets) that may be commanded remotely.

#### 1.2. State of the Art

Because every single robotic spacecraft launched from Earth is a significant investment, space agencies like NASA spare little expense to defend against the possibility that a spacecraft might fail prematurely and be lost forever. Normally, engineers defend flight computers against the risk of radiation damage or disruption by using radiation-hardened processors, like the BAE RAD750, whose circuitry is physically redesigned to resist high levels of radiation. [1] [2] Unfortunately, these specialty devices lag behind their unhardened consumer equivalents in performance, mass, cost, and power consumption. [1] [3] [4] If new research can establish a way to effectively defend off-the-shelf flight computers from radiation, it may allow engineers to design more capable software for robotic spacecraft with lower mass and power requirements.

One common approach for defending electronic systems from unexpected faults is to use *triple-modular redundancy* (TMR). [5] In a TMR design, a system includes three replicas of the critical components that all receive the same inputs and vote on every set of outputs. In the absence of radiation, all three replicas remain perfectly synchronized, and agree on exactly what output they should produce. When radiation causes a single fault, it will damage only one of the replicas, which may make that replica misbehave and start producing the wrong output. However, since the other two replicas will still agree with each other, the majority vote of the three preliminary outputs will still result in the correct final output. As long as radiation damages only one replica, and the system can repair each damaged replica before the next radiation fault occurs, the system will be able to continue operating seamlessly through an unlimited number of radiation faults. Because radiation faults occur infrequently, on the order of a few times per day (though this varies significantly based on radiation environment and specific equipment), there is generally plenty of time for the system to repair each damaged replica. [6]

Ordinarily, engineers implement triple-modular redundancy in hardware; when they implement it in software by switching rapidly between the software for different replicas, the term is *redundant multithreading*. Existing work on redundant multithreading focuses on protecting only software applications and assumes that some other approach will protect the underlying operating system. [7]

Choice of operating system is already even more essential for spacecraft computers than terrestrial computers. Flight software generally has strict subsecond deadlines to perform critical spacecraft functions, like executing the guidance algorithms that control actuators like thrusters and reaction wheels; if the software does not perform those critical functions on time, the spacecraft may malfunction catastrophically, such as by spinning out of control and breaking apart. Therefore, engineers ordinarily build flight software on top of hard-real-time operating systems, like VxWorks, INTEGRITY, RTEMS, or FreeRTOS. [1] [8] [9] These hard-real-time operating systems provide operating system abstractions similar to the abstractions provided by general-purpose operating systems like Linux or Windows, such as tasks, semaphores, queues, file systems, and dynamic memory, except that the abstractions are carefully implemented to eliminate unexpected or uncertain delays that could cause the software to exceed its strict deadlines.

Because hard real-time operating systems ordinarily run on radiation-hardened flight computers, their designs do not account for radiation concerns. This means that redundant multithreading applications running on hard-real-time operating systems will be vulnerable to radiation errors in the underlying operating system.

### 1.3. New Approach

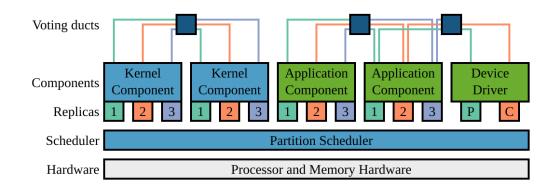

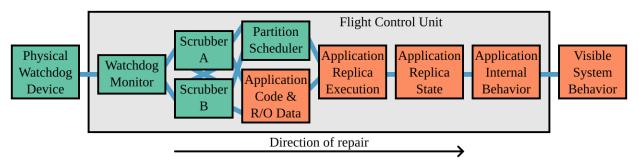

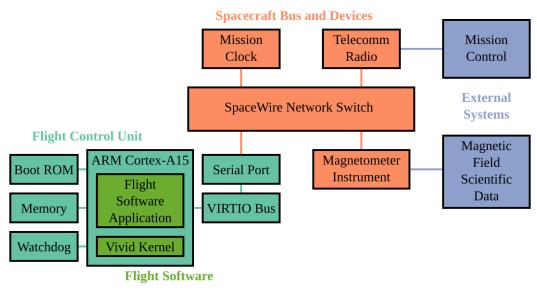

Figure 1-1: Vivid System Structure

This thesis introduces a new hard-real-time operating system, *Vivid*<sup>1</sup>, designed to run on single-core consumer ARM processors without any hardware defenses against radiation. Vivid, shown in Figure 1-1, departs from traditional real-time operating system designs in two main ways: First, Vivid uses the microkernel approach of separating out as many features from the kernel as possible into small independent modules, leaving the partition scheduler as the single fully privileged kernel component. Second, it implements a new set of operating system abstractions targeted for defending applications with redundant multithreading. These include *voting ducts*, which allow replicated applications to communicate with each other without any runtime kernel support or single points of vulnerability to radiation. (Most microkernels, by contrast, need to provide some runtime kernel support for inter-process communication.) In many cases, such as for parts of its watchdog driver, Vivid's kernel components are also replicated, just like its application components.

Vivid seeks to seamlessly mitigate almost all of the possible radiation faults that flight software might experience. It cannot seamlessly mitigate *all* possible radiation faults, because

<sup>&</sup>lt;sup>1</sup> The name "Vivid" refers to the definition of the word meaning "full of life or vitality." This references the operating system's ability to thrive in environments uninhabitable by other operating systems.

failures in critical parts of the operating system (like the scheduler) can disrupt the system's ability to function beyond the ability of software to repair the problem. In these cases, where visible failures are inescapable, Vivid uses a watchdog to ensure that the flight software will recover within a short, bounded interval of time and resume executing, possibly after a partial or complete reset of the system's state.

To evaluate whether Vivid can actually satisfy these reliability goals, this thesis presents five new systems. The first system is a prototype implementation of Vivid that runs on an emulated ARM platform. The second system is *Swivel*<sup>2</sup>, a hypothetical design for a simple testbench spacecraft with a list of representative behavior requirements. The third system is *SwivelFSW*<sup>3</sup>, which is an implementation of flight software on Vivid for the Swivel spacecraft, and the fourth system is *SwivelSim*<sup>4</sup>, which is a simulation of Swivel's avionics equipment that can evaluate the flight software against the list of behavior requirements from the design. The fifth system is *Hailburst*<sup>5</sup>, an efficient and deterministic tool for injecting radiation faults into an emulated processor. This thesis uses Hailburst and SwivelSim to evaluate the ability of SwivelFSW to satisfy its requirements in the presence of simulated radiation, and to determine how effective Vivid's design actually is at defending flight software from radiation errors.

### 1.4. Contributions and Results

This thesis makes several contributions:

1. The design of Vivid, a hard-real-time operating system for building radiation-tolerant flight software using redundant multithreading on single-core processors. It includes:

<sup>&</sup>lt;sup>2</sup> The name "Swivel" refers to the least essential element of a staffed avionics testbed: the swivel chair.

<sup>&</sup>lt;sup>3</sup> SwivelFSW is short for "Swivel Flight Software."

<sup>&</sup>lt;sup>4</sup> SwivelSim is short for "Swivel Simulation."

<sup>&</sup>lt;sup>5</sup> The name "Hailburst" refers to the accelerated fault injection features of the simulation system, and how they involve dumping a large number of potentially damaging particles over a wide area in a short period of time.

- A compile-time component initialization system for C, which allows engineers to build complex low-level software applications without dynamic resource allocation.

- b. A memory scrubber that leverages the component initialization system to protect flight software's minimum safe state.

- c. The *execution clip* abstraction for Vivid's partition scheduler, which allows seamless correction of radiation vulnerabilities in implicit register and stack state.

- d. The *voting duct* concurrency primitive that allows redundant multithreading deployments to avoid single points of vulnerability in their voting stage.

- e. The *voting notepad* for voting on redundant-multithread mutable states by treating feedforward state as a loopback message.

- f. The *prepare/commit* device driver design for radiation safety when devices are unreplicated.

- g. A *sequence of repair* to reliably ground the recovery of a complete flight software application in a hardware watchdog.

- 2. The implementation of a prototype of Vivid, which includes:

- a. *Siren*, an extended C preprocessor to facilitate instantiating software components at compile time.

- b. A *replication linker*, which allows object code in an application binary to be selectively replicated to avoid single points of vulnerability in shared code.

- 3. Hailburst, an efficient and deterministic tool for automatically injecting radiation faults into a QEMU emulation of a spacecraft processor. Compared to existing fault injection tools, it contributes:

- a. An approach to precisely target the injection of faults into QEMU without loss of emulation performance through the use of QEMU's virtual time mechanism and an emulator patch.

- 4. The design of an avionics testbench spacecraft, Swivel, which contributes:

- a. A set of devices with behavior requirements that are simpler than, but representative of, the requirements of real robotic spacecraft.

- b. The *FakeWire* protocol for tunneling a SpaceWire link over a serial port interface.

- The design and implementation of SwivelSim, a simulation for Swivel, which contributes:

- a. A tool for continuously generating test inputs, and continuously evaluating actual spacecraft behavior, to continuously report on the spacecraft's adherence to or deviation from the correct behavior indicated by Swivel's requirements, and how it changes over the course of a simulation.

- b. The *timesync protocol* that connects a processor emulated in QEMU to a spacecraft bus simulated in a separate program while maintaining complete determinism in the combined simulation.

- The design and implementation of SwivelFSW, the flight software for Swivel. It contributes:

- a. A demonstration of implementing flight software using Vivid's abstractions.

- A spacecraft bus topology using virtual network switches that treats the flight software as an extension of the network architecture, so that each software component is treated as its own device on the spacecraft bus.

- c. A flight software topology that allows several modules to send and receive command and telemetry messages without runtime registration.

- d. A set of device managers that demonstrate how engineers can implement state machines in redundant-multithreaded software components.

- e. A network device driver that demonstrates Vivid's prepare/commit driver design.

- f. A schedule that enables the efficient flow of requests and responses across a spacecraft bus without compromising on strict time partitioning.

- A preliminary evaluation of Vivid's ability to defend flight software against radiation faults, which indicates:

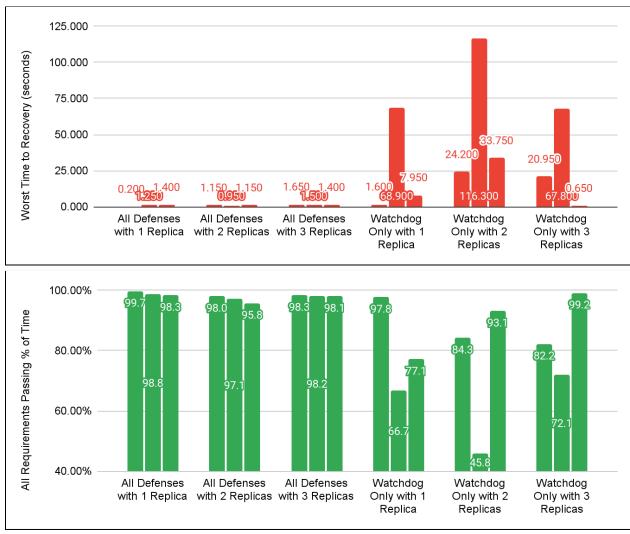

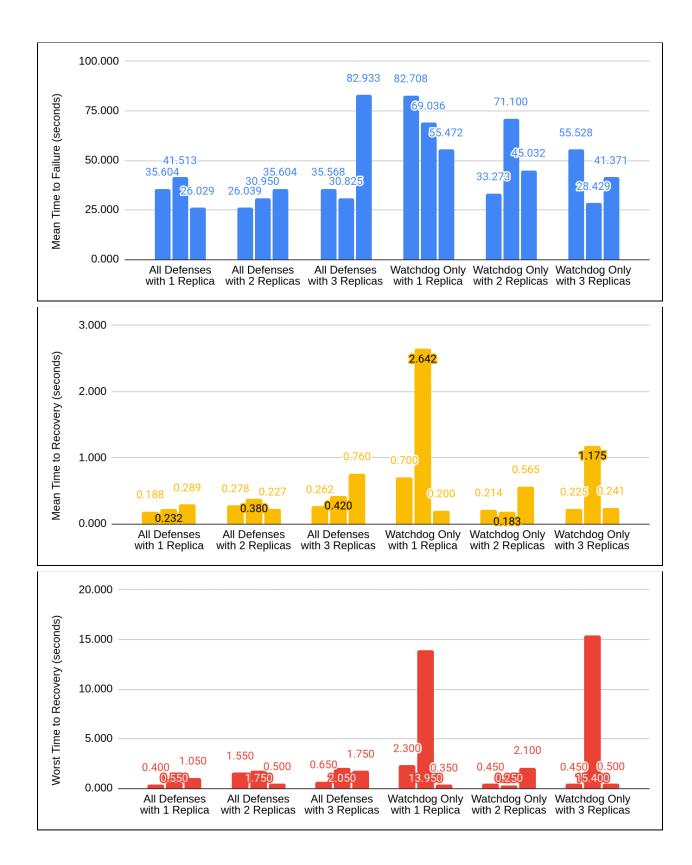

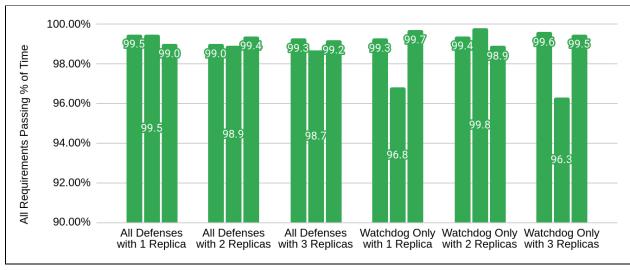

- a. Vivid is successful at seamlessly recovering from the majority of injected radiation faults without violating any behavior requirements. However, in the remaining minority of about one out of every 150 faults, it does violate one or more behavior requirements for a short time before recovering.

- b. When radiation faults lead to visible failures, Vivid's defenses consistently allow Swivel's flight software to recover back to working order within just over two seconds, which is the expected worst-case recovery time given the watchdog configuration.

- c. Vivid's other defense mechanisms appear to be more effective than the redundant multithreading system itself. Further evaluation and analysis will be required to determine which of Vivid's design features are most essential, and iterations on Vivid's design may improve the effectiveness of the redundant multithreading system.

### 1.5. Source Code Overview

The source code for all of the components in this thesis is available online on GitHub. The bulk of the code for Vivid, Hailburst, Swivel, SwivelFSW, and SwivelSim is available under <u>https://github.com/celskeggs/hailburst</u>, and is not yet separated neatly into separate modules. (The patches to QEMU are available at <u>https://github.com/celskeggs/qemu</u>.) Table 1-2 provides an overview of the number of lines of code written as part of this thesis.

| Lines of Code | Source Module                   |

|---------------|---------------------------------|

| 6,519         | SwivelFSW                       |

| 8,685         | SwivelSim                       |

| 4,997         | Vivid                           |

| 1,646         | Hailburst                       |

| 4,538         | Analysis Tools                  |

| 1,059         | Linux support code <sup>6</sup> |

Table 1-2: Source Code Breakdown

### 1.6. Outline

This thesis proceeds as follows: Section <u>2. Related Work</u> describes the existing work in defending spacecraft avionics from radiation errors and injecting faults into avionics simulations; Section <u>3. Design of the Vivid Kernel</u> explains the design of Vivid and all of its abstractions and safety properties; Section <u>4. Implementation of the Vivid Kernel</u> explains the prototype implementation of Vivid; Section <u>5. The Swivel Spacecraft</u> describes Swivel's design and requirements; Section <u>6. The SwivelFSW Flight Software</u> describes the SwivelFSW flight

<sup>&</sup>lt;sup>6</sup> The Linux support code is code that can be compiled together with SwivelFSW to make a version of the flight software that runs on embedded Linux, instead of Vivid. It is not a major component described in this thesis.

software; Section <u>7. The SwivelSim Avionics Simulation</u> describes the simulation of Swivel's avionics; Section <u>8. The Hailburst Fault Injection System</u> describes Hailburst's design and implementation; Section <u>9. Evaluation</u> explains the results of the preliminary evaluation of Vivid's reliability; and, finally, Section <u>10. Future Work and Summary</u> discusses directions for future work on Vivid's design and evaluation.

### 2. Related Work

Section <u>2.1. Radiation Defense</u> discusses existing approaches to defending flight software against radiation errors, and how Vivid differs from them. Section <u>2.2. Fault Injection</u> discusses existing approaches to fault injection, and how Hailburst differs from them.

### 2.1. Radiation Defense

Defenses for radiation faults fall into four categories: 1) hardware implementation defenses, such as radiation-hardened computers, 2) software implementation defenses, such as special compilers that insert redundant computations, 3) hardware architecture defenses, such as combining multiple separate processors in a redundant configuration, and 4) software architecture defenses, such as replicating software into multiple running processes on a single processor. Vivid falls into the software architecture defense category.

Hardware implementation defenses, such as those used for the BAE RAD750, are well-established, but radiation-hardened computers have lower performance, higher cost, higher power consumption, and higher mass requirements compared to off-the-shelf alternatives. [1] [3] [4] [10] Vivid, like many other research projects, seeks to help mitigate these challenges by defending off-the-shelf hardware.

The ASCOT testbed on the ARGOS satellite used two software implementation defenses, EDDI (Error Detection by Duplicated Instructions) and CFCSS (Control-Flow Checking by Software Signatures), and one software architecture defense, a memory scrubber, to defend an off-the-shelf processor from radiation errors. [11] Vivid also uses a memory scrubber, but not instruction-level code modifications; while these approaches improved the reliability of the

off-the-shelf processor used in ASCOT, the experiment still experienced a significant number of silent data corruptions, hangs, and crashes, suggesting that other defenses will be required to effectively defend a system.

CEDA is an example of a newer iteration of the same control-flow checking approach from the ASCOT testbed, of which it is only one of many. [12] It aims to maximize the number of errors that can be detected while minimizing the performance overhead of the technique. It only detects radiation errors, and does not correct them. Vivid, by contrast, accepts a high performance penalty by using Redundant Multithreading in exchange for detecting and correcting as many faults as possible.

The CALIPSO mission used a quadruple-replicated off-the-shelf processor as its primary flight controller. [6] This is an example of a hardware architecture defense; it did not require significant modifications to the flight software, but instead relied on hardware voting to protect against processor errors, and hardware-based EDAC (error detection and correction) to protect against memory errors. Vivid, by contrast, attempts to operate correctly even when the processor and main memory are unprotected from radiation faults.

The SpaceCube RHBSW (Radiation Hardening By Software) techniques include checkpoint-and-restart, control-flow assertions (like in CEDA or ASCOT), and watchdog timers. [5] Vivid also implements the use of a watchdog timer, but doesn't support checkpoint-and-restart techniques, which are appropriate for scientific computing software, not flight control software; attempting to roll back a guidance software control loop to a previous state would violate its real-time requirements.

The ADDAM (Adaptive Dependable Distributed Aerospace Middleware) platform is a system for distributing fault-tolerant software, which supports the hardware architecture defense

of distributing software across computers. [13] However, ADDAM depends on the Raft consensus algorithm to coordinate separate machines, which tolerates only disconnections and crashes, not silent data corruptions. [14] Further, it is not clear how ADDAM might support hard-real-time requirements, nor whether it intends to. By contrast, Vivid is a hard-real-time operating system, and intends to prevent silent data corruptions entirely.

The AIR operating system is a real-time operating system based on time and space partitioning, which is an example of a software architecture defense. [15] It separates different parts of flight software by function, and places them in independent partitions with independent operating system kernels. Like Vivid, it switches between partitions only on a sequence of fixed time slices; however, it is not intended to address radiation challenges, and its radiation defense is limited to protecting partitions from errors in other partitions.

Romain is an operating system service for the Fiasco.OC microkernel, which transparently replicates a binary application using Redundant Multithreading. [7] It is an example of a software architecture defense similar to Vivid; however, Romain is not designed for real-time applications, which makes it inapplicable to flight control software, and it does not defend itself or the Fiasco.OC microkernel against radiation errors, so there is a significant hole in its possible reliability.

Theseus is an operating system written in Rust that improves the modularity of an operating system by reducing the amount of state held for one component by another. [16] Among other goals, Theseus uses this structure to help it recover from kernel-level hardware faults, such as radiation errors. Like Vivid, Theseus splits the operating system into many small components that hold minimal state, but Theseus relies on Rust's language safety features for

recovery, which can be undermined by radiation errors, and it does not include any specific support for executing redundant software applications.

### 2.2. Fault Injection

Existing fault injection tools are difficult to use to evaluate the reliability of Vivid and its flight software, for a number of reasons. First, many fault injection tools have not been published, depend on unavailable proprietary tools, depend on the accessibility of physical devices to test, or no longer compile or function correctly on modern operating systems due to a lack of maintenance. Second, many fault injection tools feature designs that limit simulation performance compared to that of the underlying emulator, which makes them inapplicable to full-system simulation. Third, some fault injection tools bias the times or locations where they inject faults; this skews the fault injection results in unpredictable ways. Hailburst avoids these failure modes to the extent possible.

The majority of fault injection tools do not use software simulations. Some systems require a physical copy of the processor and inject faults through the use of accelerated radiation sources, pulsed lasers, or JTAG ports. Other systems use FPGAs, either to allow access to processor state, or to instrument processor circuitry with fault injection capabilities. Quinn et al provides an overview of several varieties of these tools. [17] Physical hardware-based solutions can be very efficient, because they can run at full realistic execution speeds, but they are very opaque: it is possible only to instrument physical devices to the extent allowed by their debugging interfaces. By contrast, appropriate changes to the source code of a software simulation will allow any aspect of a software simulation to be instrumented. FPGA systems are

easier to instrument than physical systems, but depend on the availability of realistic processor designs that can be instantiated in the gate array; many processor designs are proprietary and not generally available. Hailburst uses a software simulation both for versatility and to avoid the need for specialized hardware.

FEMU is an instruction-level fault simulation tool based on QEMU. [18] QEMU is a virtual machine host that uses dynamic binary translation to efficiently virtualize guest machines. [19] FEMU simulates permanent faults, intermittent faults, and transient faults by forcing QEMU into single-step mode, which allows it to modify registers and memory after every single instruction. QEMU's standard single-step mode, measured independently of FEMU's actual implementation, degrades the execution speed of QEMU significantly; the performance of simulating the Linux kernel boot process drops by nearly 65% in single-step mode, not even counting the impact of running FEMU's fault injection code on every single instruction.

DRSEUS is an instruction-level fault simulation tool based on Simics, a proprietary full-system simulation tool. [20] It takes advantage of the Simics checkpoint file format to dump system states to disk, mutate checkpointed state to inject bitflips, and resume execution from the mutated state. Because Simics is proprietary, it was not readily usable for this thesis, and because simulation checkpoint formats are generally highly specialized and not easily inspected, the same approach is difficult to apply to other simulation systems. QEMU, for example, stores its checkpoints as an extension to the QCOW2 disk format, but the details of the VM state in the snapshots are not documented, which makes it difficult to inject bitflips into the state without potentially corrupting the data structures of QEMU itself. [21]

FIG-QEMU is a fault injection platform based on QEMU that takes advantage of the existing debugging interface between QEMU and GDB to inject single-bit errors into the guest

virtual machine. [22] This is an efficient solution, except that it only supports injecting a single error per execution; in a complex piece of off-the-shelf software, like Linux, most of these errors will not produce any observable errors, so the limitation of only injecting one fault per execution makes this tool prohibitively slow, even though the actual execution is fast. In addition, FIG-QEMU uses clock-time offsets to decide when to inject faults; the interruption of an executing QEMU process from the outside biases the faults injected: moments when QEMU pauses (such as to translate additional binary code) will receive disproportionately many faults, whereas instructions in the middle of long translated blocks will receive disproportionately few.

FAIL\* is a fault injection tool designed with a flexible architecture, built on top of the Bochs and gem5 simulators. [23] gem5 is an inherently slow simulation tool; it is designed for processor architecture research, and executes much less quickly than a dynamic binary translator like QEMU. For its Bochs backend, FAIL\* uses an instrumentation system based on a programming language called AspectC++, which allows experiments to listen for particular Bochs events, such as instruction execution and memory access. Unfortunately, this instrumentation takes an already-slow Bochs and makes it slower. Further, FAIL\*'s standard fault injection campaigns involve analyzing a complete trace of a test program; during an experiment with running Linux, FAIL\* produced multiple gigabytes of trace data before the kernel had even finished decompressing. This combination of factors means that FAIL\* is not suitable for continuously injecting faults into a large and complex piece of software like Vivid.

Hailburst resembles FIG-QEMU most closely, in that it uses QEMU and GDB's existing debugging interface for injecting bitflips. It extends the approach by supporting injecting multiple radiation faults within a single execution, and by precisely targeting injected faults to

eliminate any clock-time bias from its fault injections. It is also open source and available at <a href="https://github.com/celskeggs/hailburst/">https://github.com/celskeggs/hailburst/</a>.

# 3. Design of the Vivid Kernel

Vivid provides a framework for building radiation-tolerant applications with redundant multithreading. The resulting applications are tightly coupled to Vivid, which allows the combined system to precisely manage its radiation vulnerabilities. Section <u>3.1. Redundant</u> <u>Applications on Vivid</u> describes how replicated applications function on Vivid. Section <u>3.2.</u> <u>Structure of Vivid's Kernel</u> depicts the structure of the Vivid kernel itself. Section <u>3.3. Vivid API</u> <u>Overview</u> provides an overview of Vivid's memory, communication, and execution abstractions that serve the needs of replicated applications. Section <u>3.4. Output and State Voting</u> describes how Vivid supports safe redundant multithreading using its voting and scheduling abstractions. Section <u>3.5. Static Component System</u> describes the static component system that allows engineers to combine applications together with Vivid at compile time to support effective repair and recovery at runtime. Finally, Section <u>3.6. Safety Properties</u> describes how Vivid establishes its safety guarantees, particularly the guarantees that applications can recover seamlessly from most radiation faults, and that Vivid helps applications prevent serious malfunctions even in the cases where seamless mitigation is not possible.

### 3.1. Redundant Applications on Vivid

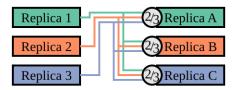

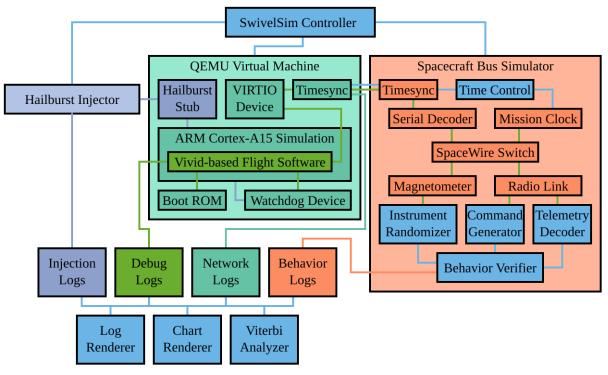

Figure 3-1: A simplified diagram of flight control software implemented using Vivid

Figure 3-1 depicts a simplified design of radiation-tolerant flight software for a spacecraft. This abbreviated design features a single spacecraft bus accessible through a memory-mapped network device, and three device managers (for a radio, a magnetometer, and a mission clock) that communicate with their corresponding devices on the spacecraft bus through a network driver and two virtual network switches. In this example, the flight software engineer implemented the application's functionality by separating out the different parts of the software into six communicating components, which are each replicated individually. The application should be immune to silent data corruptions<sup>7</sup> in its main components, and can usually continue to operate seamlessly in the presence of continuous radiation, but it is possible for rare radiation

<sup>&</sup>lt;sup>7</sup> Silent data corruptions refer to radiation errors that modify a piece of data without causing a visible crash. An example is an error where a sensor reading is corrupted from the real value to another value that is technically valid, but not the actual value measured. If it were corrupted to an invalid value, by contrast, it would be detectable.

faults to temporarily cause part or all of the application to crash. Vivid will automatically recover from crashes and restore affected parts of the application to operation, but the application may lose some or all of the data it was storing or processing.

An engineer composes a Vivid application from a set of components, some standardized and some unique, and connects them together in a configuration appropriate for the requirements of the spacecraft system. She may define components directly, compose them from smaller components, or both. Vivid will instantiate each component and subcomponent in complete detail at compile time, allocate all of their resources, and predetermine all of their connections. Because applications require minimal initialization at runtime, Vivid can efficiently recover from radiation errors: in many cases, Vivid can repair damage by overwriting the damaged region of memory with the initial version of the region from the boot image. If Vivid did not predetermine the exact resources and interconnections for the damaged component, it would not be able to determine the correct repairs to make, and would need to reinitialize the whole application whenever any portion needed to be repaired.

In the simplified flight software shown in Figure 3-1, each of the application components is composed of three replicas in a redundant configuration, which allows each component to operate seamlessly as long as two of the three replicas are undamaged. The downstream components that receive data from a replicated component will compute a 2-out-of-3 vote over the outputs provided by the replicas, so that they can seamlessly conceal the incorrect behavior of any single transmitting replica. Vivid uses a partition scheduler to ensure that replicas execute in lockstep, so that timing discrepancies will not cause spurious disagreements. Once an error occurs in a component, that component must correct the error quickly, so that it is vanishingly

unlikely that a second radiation fault will occur before the first fault is repaired. Section <u>3.6.</u> <u>Safety Properties</u> discusses the safety guarantees that are possible under Vivid's voting system.

### 3.2. Structure of Vivid's Kernel

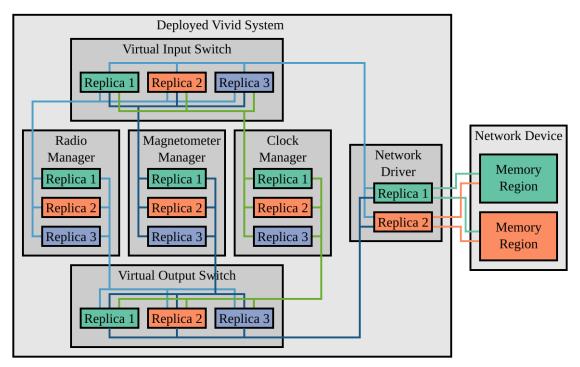

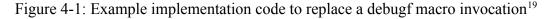

Figure 3-2: A diagram of the kernel components present during runtime.

The components instantiated for a particular application execute alongside Vivid's kernel components. Figure 3-2 depicts the components that implement each of Vivid's responsibilities and how they relate to the application itself. The first responsibility of Vivid's kernel is to maintain the system image in volatile memory, which it does through a bootloader and a memory scrubber. When the system powers up or experiences a reset, the bootloader defined in nonvolatile memory loads the boot image into volatile memory; once the partition scheduler starts running, it executes a memory scrubber that continuously reviews the current contents of memory and ensures that they match the original image. Vivid executes two replicas of the

scrubber, rather than only one, so that they can repair each other. Because Vivid applications are initialized at compile time, rather than runtime, the scrubbers can protect applications' read-only data without explicit registration. However, because the scrubber can repair errors only in read-only memory (including executable code), but not errors in writable memory (such as application state), applications are responsible for defending their own writable memory.

After the bootloader loads the initial kernel image, and Vivid and the application perform any device initialization they require, Vivid proceeds into the partition scheduler. Vivid executes application and kernel code according to a rigid predefined schedule to provide the determinism needed for voting to proceed in lockstep. The schedule specifies the exact order in which replicas and components execute code and exactly how long they execute for; it repeats indefinitely as long as the system is powered on and operational, one scheduling cycle at a time. If a replica cannot complete its execution by its deadline, the partition scheduler forces it to crash and schedules the next component immediately. The partition scheduler will resume crashed replicas from a safe entry point after the memory scrubber has a chance to repair any errors in their code and read-only memory.

In order to ensure that the system remains operational, a physically-isolated and radiation-hardened watchdog device monitors Vivid's execution. As long as the application and operating system agree that the system is operating normally, the watchdog monitor component will feed the watchdog device on a regular basis. An engineer assigns a deadline to each aspect of the system monitored by the watchdog, and sets each deadline to a long enough interval that the components have a chance to recover from any radiation faults they experience. However, if any component fails and does not recover by its deadline, the watchdog monitor will assume that something has gone irreparably wrong, and ask the watchdog device to force a complete reset of the processor.

Alternatively, if the system is irreparably damaged, and the watchdog monitor cannot request a reset, the watchdog device will notice that it has not heard from the monitor recently enough, and forcibly reset the processor. After it triggers the processor reset, the bootloader will reload the entire application, and the system will reinitialize from a safe state. Because the whole system will be inoperational until the restart is complete, and application data may be lost in the process, Vivid only relies on the watchdog as a repair mechanism of last resort. Although Vivid uses safer and less disruptive repair mechanisms when possible, it still employs a watchdog, because a watchdog device works even in the case that the entire kernel hangs and no repair code at all can run.

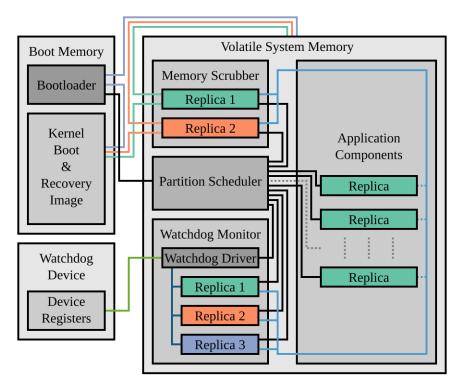

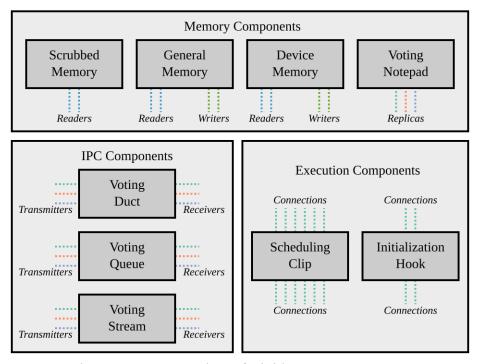

#### 3.3. Vivid API Overview

Figure 3-3 provides a brief overview of Vivid's core API, in the form of the built-in components that are available for engineers to instantiate to build their applications. First is the category of memory components, which represent memory regions with different properties. *Scrubbed memory* is immutable, and allows the memory scrubbers to automatically repair any errors in it within one recovery period. This is especially useful for configuration data structures. *General memory* is mutable and not automatically scrubbed. It is useful for replica-local data structures and replica-local data buffers, but requires the individual replicas to take responsibility for error detection and recovery. *Device memory* provides read-only or read-write access to memory-mapped device registers, and is a necessary part of driver components for memory-mapped devices. *Voting notepads* act like general memory, but they automatically

resynchronize their state across a set of replicas by a majority vote on each scheduling cycle, and place less responsibility for error recovery on the application.

Figure 3-3: An overview of Vivid's core components

The second category is composed of the IPC components. A *voting queue* is a single-reader-single-writer FIFO queue used to reliably communicate between two replicated components, with support for backpressure if the queue fills up. A *voting duct* is a simplified version of a voting queue that does not support backpressure; instead, the receiver must always be ready to immediately process or discard a number of messages equal to the capacity. A *voting stream* is a byte-oriented variant of a voting queue.

The third category is composed of the execution components. Engineers can make code runnable under the partition scheduler by defining an *execution clip* and placing it in the partition schedule. The partition scheduler calls the main function associated with each clip once in each scheduling cycle and allows it to run for up to a configured maximum execution time. To

facilitate device initialization, engineers can also attach code to initialization hooks. Vivid will execute each hook in turn during the boot process and allow each hook to run to completion before starting the partition scheduler.

### 3.4. Output and State Voting

Vivid supports output and state voting to enable redundant multithreading in applications, but it does not implement any features for this directly in the kernel. Instead, Vivid's IPC library implements the functionality: The IPC library implements voting ducts directly on top of Vivid's shared memory and partition scheduling primitives, and implements voting queues and voting streams in terms of voting ducts. Voting ducts are single-reader single-writer FIFO queues, like voting queues, except that they do not support indicating backpressure; because a duct receiver cannot apply backpressure, it cannot refuse data transmitted over a duct, which eliminates the requirement for bidirectional voting. Ducts will vote on transmitted messages, but not on whether the recipients can handle additional data. Voting queues reintroduce backpressure by augmenting a main voting duct with a backwards voting duct that indicates whether the receiver can accept additional messages. Separating out voting ducts from voting queues has two advantages: first, if a transmitting component knows that a receiving component will always be able to accept data immediately, it does not need to consider what to do in the case that it cannot transmit data, and second, the implementation of voting queues is simpler, because the two votes are cleanly separated from each other.

To ensure that transmitters cannot overwhelm receivers with an unexpectedly large number of messages, engineers define each voting duct with a specific maximum message size and transfer rate. Voting ducts will refuse to accept more messages than allowed within each

scheduling cycle, which allows engineers to design receivers to only handle the maximum transfer rate each scheduling cycle. Because the flow of data to any one of the receiver replicas does not depend on the behavior of the other receiver replicas, a malfunction in one receiver replica will not affect the ability of another replica to receive data.

Engineers must also specify maximum message sizes and transfer rates for voting queues, but the transfer rates are further limited to the number of messages indicated by the receivers through the backpressure duct. Vivid implements voting streams as single-element voting queues that transport all data for each scheduling cycle as a single message.

Figure 3-4: Embedded voter architecture.

Voting ducts allow Vivid to vote on component outputs in a distributed rather than centralized fashion, as shown in Figure 3-4, to reduce the number of single points of vulnerability in the system. The engineer defines each application component to have three replicas, and each replica writes its vote of the correct output messages to its own individual buffer each time it executes, using the voting duct API. Each of the downstream replicas that receives data from the upstream component will independently read the messages from each buffer, determine which messages form the majority, and proceed using that majority result as its input. By embedding the voters into the downstream replicas, Vivid avoids the creation of a single voter point of failure: radiation faults that occur during voting will be detected and corrected by the voters that vote on the downstream component's replicated outputs. Because two replicas, if they agree, will overrule any output from a third replica, voting ducts allow Vivid to silently mask any component output errors, including silent data corruptions, as long as they only affect a single replica's behavior.

Engineers can employ voting ducts (and higher-level voting abstractions) in any arrangement of components, as long as they can design every component to be triply-replicated. Performing each vote three times may make it non-obvious from an exterior point of view which voting outcome is the "true" outcome, but Vivid only needs to establish a single true outcome of a vote when a device driver needs to interact with a single-replicated device; it is otherwise unnecessary.

Voting ducts handle vote splits, such as where the three replicas disagree on the next message (or whether there should be a next message at all), by dropping the data at the offending offset in the message buffer, and allowing the replicas to try again to reach agreement during the next scheduling cycle. Voting queues and streams treat vote splits on the backpressure vote as an indication that the recipients cannot receive any data, and wait until the vote is resolved before continuing to transmit.

A component using backpressure voting needs to account for the possibility that one of its replicas may receive data even when it indicated in the previous scheduling cycle that it could not accept any. This condition can occur when the backpressure vote encounters a 2-1 vote split, with the majority in favor of receiving more data. An engineer must design their components to handle this case, such as by entering the replica into a safe failure state and resynchronizing its mutable state against the other replicas when possible. In particular, she must ensure that backpressure disagreements do not prevent the component from resynchronizing.

#### 3.4.1. Lockstep Scheduling

Vivid executes all components in lockstep using a partition scheduler to synchronize the inputs and outputs transferred between components in the system. Synchronization allows components to compute replicated outputs from matching inputs and state, so that vote splits do not occur simply as a result of natural changes in inputs and state over time. Every replica is responsible for servicing every connected voting duct (or higher-level component) on every scheduling cycle, regardless of whether it transmits or receives any messages that cycle. Servicing includes reading all received data, writing any transmitted data, and updating any internal synchronization state in the voting ducts. As long as each engineer configures every execution clip with a long enough deadline, regular servicing of the voting structures ensures that any possible natural timing discrepancies (such as those caused by microarchitectural processor details) will not affect the correct execution of any of the replicas. An engineer must configure the partition scheduler with a number of clock cycles for each replica's execution clip that accommodates the worst-case code path possible in the clip, so that replicas will only ever overrun their deadlines if they are affected by a radiation error; otherwise, a series of unlucky timing discrepancies could cause a 3-way split vote to occur even in the absence of any radiation faults.

To simplify code path analysis, Vivid only supports implementing device drivers using polling, and does not support device interrupt handlers. Otherwise, a series of interrupts that arrive at an inopportune time might cause timing discrepancies that escalate into a split vote even in the absence of radiation.

#### 3.4.2. State Resynchronization

While voting ducts seamlessly mask radiation errors within a single replica, radiation errors will ordinarily persist inside the replica's state until a repair mechanism corrects them. If an engineer does not implement a mechanism to promptly repair internal errors, there is a danger that a radiation error in one replica of a component might persist for long enough that a second radiation fault could occur in another replica of the same component, leading to a three-way vote split and an externally-visible disruption. Vivid's memory scrubber repairs radiation errors in read-only memory, as long as the application marks the memory appropriately, but engineers of each component with read-write memory are responsible for implementing an appropriate mechanism to correct errors in the mutable state. An engineer might consider the use of voting notepads or *natural convergence* as effective solutions to the problem.

Vivid's support libraries provide voting notepads as a variation on voting ducts. Voting notepads write the state of each replica to a corresponding transmission buffer at the end of each scheduling cycle, and read all replicas' transmissions back at the start of the next scheduling cycle, so that they can compute a majority vote. The voting notepad places the winning result into the next transmission buffer, where the replica can read or write its contents like an ordinary region of memory, and where the replicas can read it again for voting at the start of the next cycle. This approach allows engineers to move part or all of a replica's local storage out of the replica, and extends the seamless masking property of voting ducts to become a seamless correction property of the component's state. Voting notepads will wipe away any error in the protected state by the next scheduling cycle, as long as the error is only present in one replica. It is still possible for a vote split to occur in the presence of unexpectedly high levels of radiation;

in this case, the voting notepad will indicate to the replica code that a split vote has occurred, and the replicas will need to reset their local state to a matching safe value.

Unlike regular ducts, voting notepads store two copies of the transferred state at a time, to ensure that an earlier-executing replica does not overwrite data needed for a later-executing replica to compute the same vote. Voting notepads include an additional set of variables to track which buffer is in use, and they vote on which set of buffers to use for reading and which set of buffers to use for writing before performing the data vote.

Engineers can use *natural convergence* to protect components that need to store large amounts of data for only a short time, especially when the time it would take to vote on the entire state might be too long to allow the use of a voting notepad. An example of such a component would be a telemetry collector component that combines data from many sources and buffers it temporarily until the radio can downlink it from the spacecraft.<sup>8</sup> Natural convergence observes that if one of the three replicas for this component has lost the state for the telemetry buffer, but is still tracking matching metadata for the buffer, the discrepancy between the replicas will only last until they transmit the telemetry buffer. Any new data the replicas receive will match, and the three replicas will quickly converge on a state where they continue to store the newly received data, and do not store the old data, because they have already transmitted it. Any output errors caused by the missing state will only affect a single replica, so Vivid will mask them.

Natural convergence will take longer to correct discrepancies than voting on the entire state of the component, but convergence only needs to occur before the next radiation fault that affects the component, so an engineer may decide that the increased efficiency is the correct tradeoff to make.

<sup>&</sup>lt;sup>8</sup> This example assumes that a spacecraft does not buffer telemetry in nonvolatile memory, which is often not a realistic assumption, but simplifies this explanation.

When an engineer uses natural convergence, she must take care to ensure that the component's algorithm can only converge to a single possible state; if there are multiple possible states that could be reached, different replicas might converge to different states and fail to reach agreement.

3.4.3. Voting Duct Structure

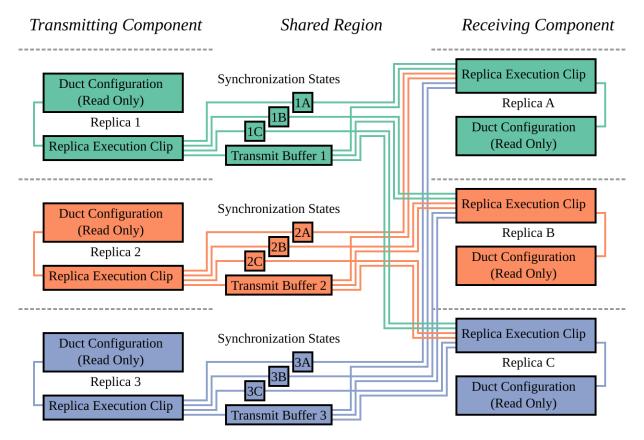

Figure 3-5: Example 3x3 Voting Duct Connectivity Diagram

Figure 3-5 outlines the structure of the voting ducts provided by Vivid's IPC library, using the common example of a duct that connects three upstream replicas to three downstream replicas. The IPC library stores the configuration for the duct itself in read-only memory, with one copy for each replica, and the voting duct API writes each message to a single transmit buffer corresponding to the transmitting replica. Each upstream replica places metadata about the number of messages it transmitted in three of the nine synchronization state variables at the end of the execution of its scheduling clip; the synchronization variables are cleared by the matching receivers to allow each replica to track which of its communication partners actually executed within the preceding cycle. The receiver clips require the synchronization information to determine which transmit buffers contain data that they should consider during voting, and both the transmitter and receiver clips additionally use the synchronization information to report warnings if their communication partners stop executing.

Each voting duct computes votes on a per-message basis, starting at the first message index and proceeding until either A) it receives the maximum number of messages configured on the duct, B) a majority of transmitter replicas agree that the transmission is complete, or C) it discovers a three-way split vote. Voting ducts *fail disconnected*; once a receiver detects a split vote, it will discard that message and all remaining messages in the current scheduling cycle, as if a fault had caused a temporary disruption in the transmitting component. If a transmitting replica clip exceeds its deadline, it is discarded from the vote.

Because voting ducts only preserve state for a single scheduling cycle, and the state does not persist over longer periods of time, they can recover from errors within a single cycle.

### 3.4.4. Replicated Components

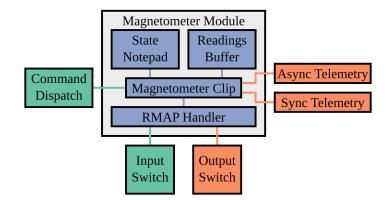

Figure 3-6: Example Replicated Magnetometer Component

Figure-3.6 depicts the structure of an example triple-replicated component that manages a magnetometer instrument. It interfaces with two input ducts and two output ducts: one input duct for commands uplinked from mission control, one output duct for telemetry downlinked back to mission control, and one input and one output duct for it to send and receive packets over the spacecraft bus for communication with the magnetometer instrument itself.

The replicas access the input and output ducts through component wrappers, which encapsulate the communication primitives in higher-level APIs; the component-specific code in the replica clip is not aware of the ducts, and instead uses APIs to receive commands, transmit telemetry, and perform network transactions (using the Remote Memory Access Protocol, or RMAP) to monitor and control the instrument.

The component stores control state about the magnetometer in a voting notepad for synchronization between replicas, and stores static configuration information in a scrubbed memory region. The component also maintains a circular buffer of magnetometer readings within each replica. The voting notepad resynchronizes itself between replicas, and the memory scrubber protects the static configuration information; the circular buffers naturally converge to empty buffers whenever the component downlinks collected scientific data as telemetry. Because the replicas operate independently, the output ducts mask the existence of any single-replica error, and because all of the state resynchronizes on a regular basis, this component satisfies Vivid's requirements for radiation safety.

#### 3.4.5. Prepare/Commit Drivers

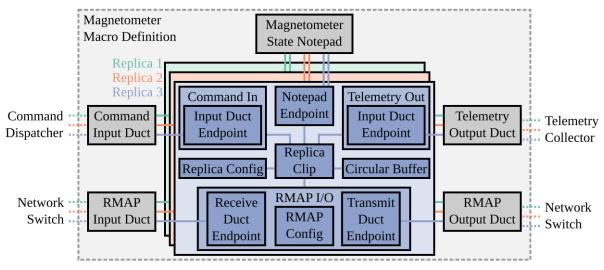

Application components can interact with external devices safely in the same way as they interact with other application components, as long as those devices contain embedded voters that can vote on the messages they receive. Unfortunately, most external devices expect single inputs, not triple inputs, and cannot calculate votes. An engineer can still design a Vivid device driver for a device that does not support voting, but the driver will be more vulnerable to radiation than a regular replicated component. For example, a damaged network driver might stop receiving or transmitting packets, might transmit or receive garbage data, might transmit or receive data from the wrong region of memory (which may be correctly-formatted, but the wrong messages), might transmit or receive more or less data than it should have, or might transmit or receive the same messages multiple times. One option for the engineer to reduce the range and severity of radiation-induced failures is to implement a prepare/commit driver, like the network driver shown in Figure 3-7. If the engineer combines a prepare/commit driver with error correction techniques used in ordinary networks, such as checksumming and sequence numbering, she might be able to implement a single network device driver vulnerable only to temporary disruption, rather than more complex data corruption.

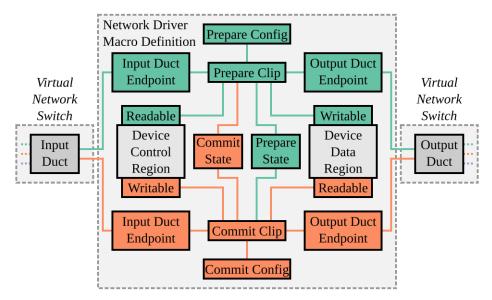

Figure 3-7: Sample Network Device Driver using Prepare/Commit Replication

Figure 3-7 demonstrates the structure of a network device driver using prepare/commit replication, which is appropriate for a network device that contains separate data and control regions. (It is common for network devices to separate data and control regions.) In this example, the network device acts as a link between a physical network interface and a virtual network switch. (The virtual network switch is responsible for routing packets within the flight software.) When the driver receives a packet from the virtual network switch, it writes the packet data to a device data region and triggers the packet's transmission using a write to the device has received a packet from the network, and when it does, it extracts the packet from the device data region and transmits it to the virtual network switch.

The prepare/commit structure separates read and write access to the device control and data regions: the prepare clip reads from the control region and writes to the data region, and the commit clip reads from the data region and writes to the control region. By separating the responsibilities for writing to either region, the design ensures that the device will only transmit a

packet if *both* the prepare and commit replicas agree on it. If one of the replicas malfunctions, the driver's transmissions will generally fall silent, rather than transmit an incorrect message. (There is an exception: depending on the details of the device's memory layout, it may be possible for the commit replica to transmit prepared packets multiple times, instead of once.) Similarly, both replicas must participate in receiving packets from the network, because they will have to both transmit the same message to the voting switch duct to win the vote: the driver's receptions will also fall silent. Neither mechanism can prevent data or length corruptions that occur when data is stored in the device buffers, but an engineer may already need to protect against the possibility of those errors occurring during transmission on the physical communications medium of the network.

# 3.5. Static Component System

To allow Vivid to fully instantiate the application and kernel components at compile time, engineers implement Vivid components using a combination of a macro system and C's existing static language constructs. For example, an engineer can instantiate a 4 KiB general-purpose memory component by defining a global variable of type uint8\_t[4096]. To instantiate a read-only memory component protected by the scrubber, she can define a global variable of type const uint8\_t[4096]. To instantiate a more complex component, like a circular buffer, she would invoke the macro for that component, such as: CIRC\_BUF\_REGISTER(buffer\_name, sizeof(element), NUMBER\_OF\_ELEMENTS).

To define a new type of application component, an engineer defines a macro parametrized by the instance name, configuration parameters, and connections, and specifies in the macro body the series of global variable definitions (or macro invocations) that instantiate the

parts of the component. Figure 3-8 demonstrates the macro definition process by composing a simplified voting queue component out of two voting duct components. (This definition omits several complexities present in the real voting queue implementation.)

In some cases, an engineer will define additional macros as part of a component definition to access specific static properties of a complex object, such as the list of clips that the partition schedule needs to include for this component, or the list of commands the component can accept from mission control. An engineer may also use C structs to define configuration and state objects associated with components, and may use regular function definitions to provide a runtime API for a component.

```

typedef const struct {

const char *label;

duct_t *dataflow;

duct_t *pressure;

} queue_t;

macro_define(QUEUE_REGISTER, identifier,

sender_replicas, receiver_replicas,

max_flow, msg_size) {

DUCT_REGISTER(symbol_join(identifier, dataflow),

sender_replicas, receiver_replicas,

max_flow, msg_size);

DUCT_REGISTER(symbol_join(identifier, pressure),

receiver_replicas, sender_replicas,

1, sizeof(bool));

queue_t identifier = {

.label

= symbol_str(identifier),

.dataflow = &symbol_join(identifier, dataflow),

.pressure = &symbol_join(identifier, pressure),

};

}

```

Figure 3-8: Simplified definition of a voting queue built using two voting ducts

Vivid uses a custom macro language, Siren<sup>9</sup>, for most component definitions, rather than using the standard C preprocessor. Siren allows engineers to define multi-line macros more cleanly than they can under the standard C preprocessor, and provides a handful of other useful features, such as compile-time loops. It also allows engineers to define custom macros using Python code, which allows Vivid to perform certain complex operations (see Section <u>4.1. Debug</u> <u>Log System</u>) at compile time instead of runtime. Because Siren still emits the same intermediate format as the standard C preprocessor, it is compatible with existing GCC-based toolchains. Vivid still uses the C preprocessor as a first stage, before Siren, to handle header inclusion and miscellaneous other preprocessing tasks, such as constant definitions.

#### 3.5.1. Static Memory Management

Because Siren ultimately reduces each instantiation of an application component to a series of global C variable and function definitions, the linker in the standard GCC toolchain can already allocate space for all memory in a Vivid system at compile time. Vivid requires engineers to allocate all memory in this way to eliminate the need for dynamic memory allocation at runtime and simplify the kernel.

Engineers can allocate shared memory (for inter-component communication) in the same way as regular general purpose memory. It becomes shared memory only because a pointer is provided to multiple execution clips. Due to time constraints, Vivid does not yet implement strict memory isolation, but a small amount of work could extend Vivid to define memory access rights at compile time.

<sup>&</sup>lt;sup>9</sup> Siren's name is a pun referring to a class of dangerous mythical creatures whose voices are famous for luring sailors to jump into the sea. I built Siren so that I could be lured back to C, instead of trying to build an entire operating system in Rust.

Engineers can reference device memory directly by hard-coding a pointer to the physical memory address at which the spacecraft circuitry maps the device memory region. Vivid discourages device drivers from dynamically discovering device addresses and configurations so that it can configure drivers at compile time as much as possible. To ensure that the application does not try to access the wrong memory regions, it is appropriate for device drivers to validate their hardcoded configurations through the standard discovery process; in the case of a mismatch, the best option is to force Vivid to reset the device and driver, and for the driver to refuse to interact with the device and loudly report an error. If the mismatch is caused by a programming error, this approach ensures that the engineer will notice the problem during testing, and if the mismatch is caused by a radiation error, retrying the discovery process after the reset will allow the driver to recover.

## 3.5.2. Execution Clips

Instead of scheduling threads, with their own registers and stacks that are saved and restored each time they execute, Vivid's partition scheduler schedules *execution clips*<sup>10</sup>. Every time the scheduler executes a clip, it enters the clip's context from the same entrypoint, by calling a main body function specified at compile-time. When the clip's body returns, the scheduler does not call it again until the next scheduling cycle. If the clip doesn't finish executing by the deadline, the scheduler forcibly terminates the execution context and discards the stack and register state. The next time the scheduler executes the clip, it starts the clip again from the regular entrypoint, not from the preemption point. This approach helps applications avoid implicitly sharing data between scheduling cycles: it is not possible for errors in register

<sup>&</sup>lt;sup>10</sup> The term "clip" comes from the term used in editing video, because an editor may play the same clip as many times as they want, but it will still depict the same things happening. This is in contrast to a standard scheduler task, which may start from a different place and perform a different operation every time the kernel schedules it.

and stack state to go unnoticed for longer than a single clip's execution, because the scheduler will discard the state containing those errors at the end of the scheduling period. (The exception is that uninitialized variables might contain state from other clips or previous executions of the same clip, but properly-implemented C code should not use the values of uninitialized variables.) Similarly, it is not possible for an unexpected delay or infinite loop caused by radiation to persist for more than a single scheduler cycle, because the partition scheduler will terminate the loop at the end of the clip's execution. The strictly deterministic execution sequence defined by the partition schedule also allows engineers to use Vivid as a hard real-time operating system; engineers can precisely analyze the behavior of any schedule to ensure that the flight software can meet its deadlines.

If the scheduler forcibly terminates a clip, either due to a timing overrun or a processor exception (perhaps caused by an access to an invalid memory address or the execution of a badly corrupted instruction), Vivid will wait until at least one of the memory scrubbers completes its next scrubbing cycle before it allows the clip to resume execution. This helps the application avoid repeatedly encountering and reporting local errors in the same replica over and over again, which would flood the debugging output of the system.

Because the partition scheduler never interleaves the execution of multiple clips (and Vivid only runs on a single processor), engineers can implement certain concurrent data structures in simpler ways on Vivid than on other operating systems. Clips do not need to acquire a mutual exclusion lock to read or modify any shared state; if the scheduler preempts the currently-executing clip in the middle of a mutation, the clip will not resume the mutation from the same point; the next clip that accesses the data structure has exclusive access, and when the first clip is scheduled again, it might start the same operation again from the beginning, but not

from the middle. The downside to Vivid's approach is that concurrent data structures become more complex in new ways: instead of needing to protect their state from simultaneous modifications, data structures must support repair of their state after modifications are aborted. If any clip begins mutating a data structure, but never finishes, the next clip to access that data structure will need to roll forward or roll backward the interrupted mutation, or detect that the structure requires repair and wait for the original clip to perform that repair. In practice, the burden of repair falls on the voting infrastructure, and most engineers writing software for Vivid do not need to consider it.

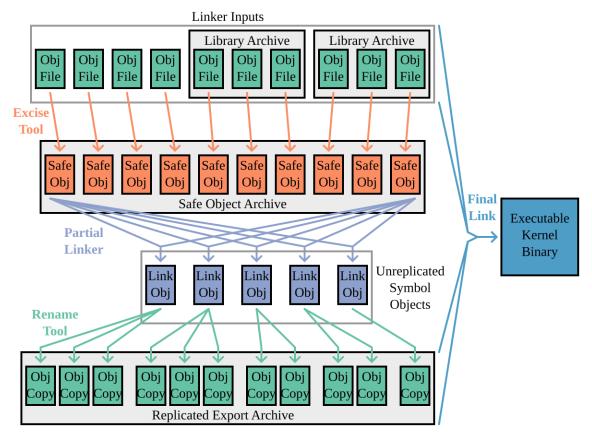

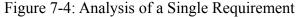

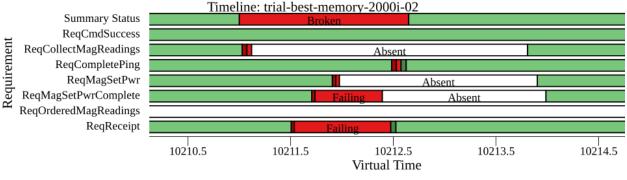

#### 3.5.3. Code Replication Linker