Table 5-1. Protected-Mode Exceptions and Interrupts

| Ve       | ctor | Mne     | Table 5-1. Protect                           |                | - LAC | cpti         |               |                                                                     |

|----------|------|---------|----------------------------------------------|----------------|-------|--------------|---------------|---------------------------------------------------------------------|

| No.      |      | mon     | ic Description                               | Туре           |       |              | Error<br>Code |                                                                     |

|          | 0    | #DE     | Divide Error                                 |                | Fault |              | Vo            | DIV and IDIV instructions.                                          |

|          | 1    | #DB     | Debug                                        | Fault/<br>Trap |       |              | <b>1</b> 0    | Any code or data reference or the INT 1 instruction.                |

| 2        |      |         | NMI Interrupt                                | Interrupt      |       | 1            | lo            | Nonmaskable external interrupt.                                     |

| 3        |      | #BP     | Breakpoint                                   | Trap           |       | N            | О             | INT 3 instruction.                                                  |

| 4        | l i  | #OF     | Overflow                                     |                | rap . | . N          | 0             | INTO instruction.                                                   |

| 5        | 1    | #BR     | BR BOUND Range Exceeded Fai                  |                | au!   | N            | 0             | BOUND instruction.                                                  |

| 6        | #    | #UD     | Invalid Opcode (Undefined Opcode)            | d Fa           | ault  | No           | o             | UD2 instruction or reserved opcode.                                 |

| 7        |      | NM      | Device Not Available (No Math Coprocessor)   | Fa             | ult   | No           | ,             | Floating-point or WAIT/FWAIT instruction.                           |

| 8        | #    | DF      | Double Fault                                 | Ab             | ort   | Ye.          | s<br>ero)     | Any instruction that can generate an exception, an NMI, or an INTR. |

| 9        |      | -       | Coprocessor Segment<br>Overrun (reserved)    | Fa             | ult   | No           |               | Floating-point instruction. <sup>2</sup>                            |

| 10       | #7   | rs      | Invalid TSS                                  | Fau            | ult   | Yes          | ,  .          | Task switch or TSS access.                                          |

| 11       | #1   | NP      | Segment Not Present                          | Fau            | Fault |              | . 1           |                                                                     |

| 12       | #8   | s l     | Stack-Segment Fault                          | _              | Fault |              |               | Loading segment registers or accessing system segments.             |

|          |      |         |                                              | rau            |       |              | 5             | Stack operations and SS register pads.                              |

| 13       |      |         | General Protection                           | Fault          |       | Yes          | A             | ny memory reference and other rotection checks.                     |

| 14       | 1    |         | Page Fault                                   | Faul           | t     | Yes          | - 1           | ny memory reference.                                                |

| 15       | -    | - 1     | (Intel reserved. Do not use.)                |                |       | No           |               | , 1121311301                                                        |

| 16       | #M   |         | x87 FPU Floating-Point<br>Error (Math Fault) | Faul           | t     | No           | x8<br>W       | 87 FPU floating-point or AIT/FWAIT instruction.                     |

| 17       | ""   |         | Alignment Check                              | Fault          |       | Yes<br>(Zero | Ar            | ny data reference in memory. <sup>3</sup>                           |

| 18       | #M0  |         | flachine Check                               | Abort          | :   1 | Vo           | Eri           | ror codes (if any) and source<br>e model dependent.                 |

| 19       | #XF  | È       | IMD Floating-Point<br>xception               | Fault          | 1     | 1            |               | E and SSE2 floating-point tructions                                 |

| -31      |      | Ir      | ntel reserved. Do not use.                   |                |       |              |               |                                                                     |

| 2-<br>55 |      | U<br>re | ser Defined (Non-<br>served) Interrupts      | Interru        | ıpt   |              | Ext           | ernal interrupt or INT n                                            |

- The UD2 instruction was introduced in the Pentium Pro processor.

IA-32 processors after the Intel386 processor do not generate this exception.

This exception was introduced in the Intel486 processor.

This exception was introduced in the Pentium processor and enhanced in the P6 family processors.

This exception was introduced in the Pentium III processor.

## intel®

## INTERRUPT AND EXCEPTION HANDLING

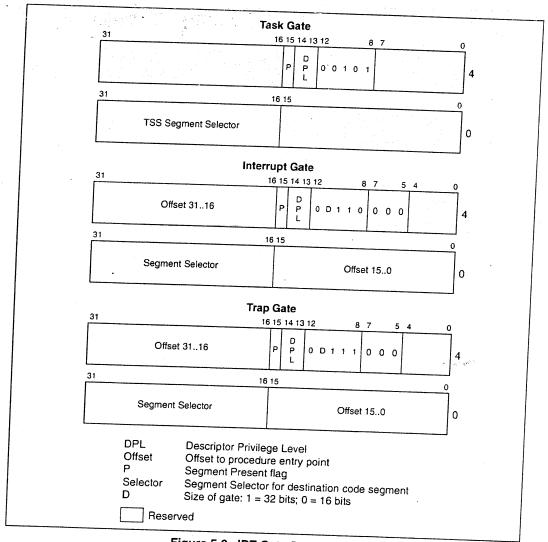

Figure 5-2 shows the formats for the task-gate, interrupt-gate, and trap-gate descriptors. The format of a task gate used in an IDT is the same as that of a task gate used in the GDT or an LDT (see Section 6.2.4., "Task-Gate Descriptor"). The task gate contains the segment selector for a TSS for an exception and/or interrupt handler task.

Interrupt and trap gates are very similar to call gates (see Section 4.8.3., "Call Gates"). They contain a far pointer (segment selector and offset) that the processor uses to transfer program execution to a handler procedure in an exception- or interrupt-handler code segment. These gates differ in the way the processor handles the IF flag in the EFLAGS register (see Section 5.12.1.2., "Flag Usage By Exception- or Interrupt-Handler Procedure").

Figure 5-2. IDT Gate Descriptors

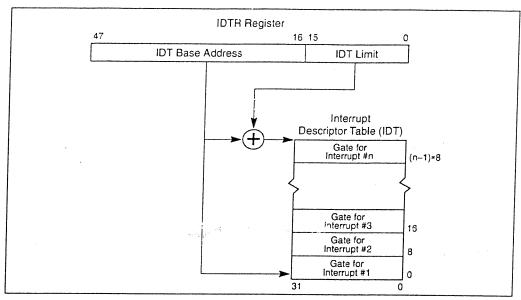

Figure 5-1. Relationship of the IDTR and IDT

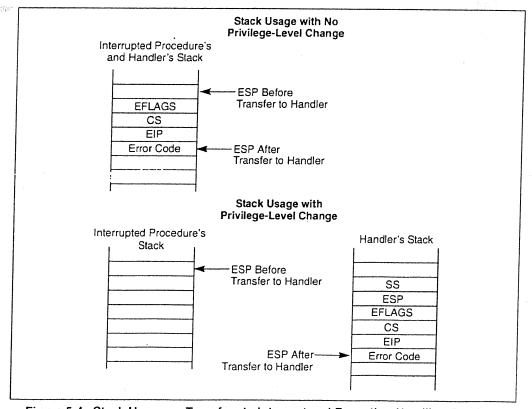

Figure 5-4. Stack Usage on Transfers to Interrupt and Exception-Handling Routines